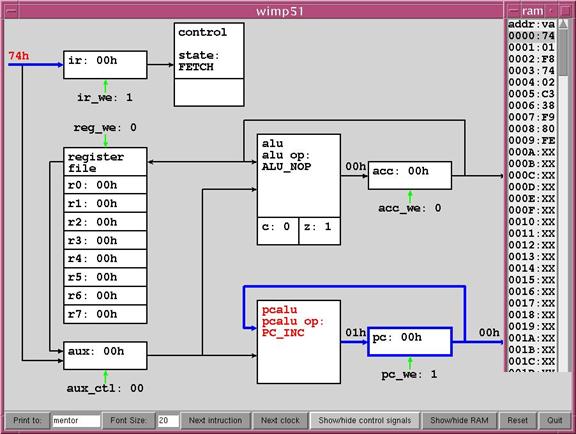

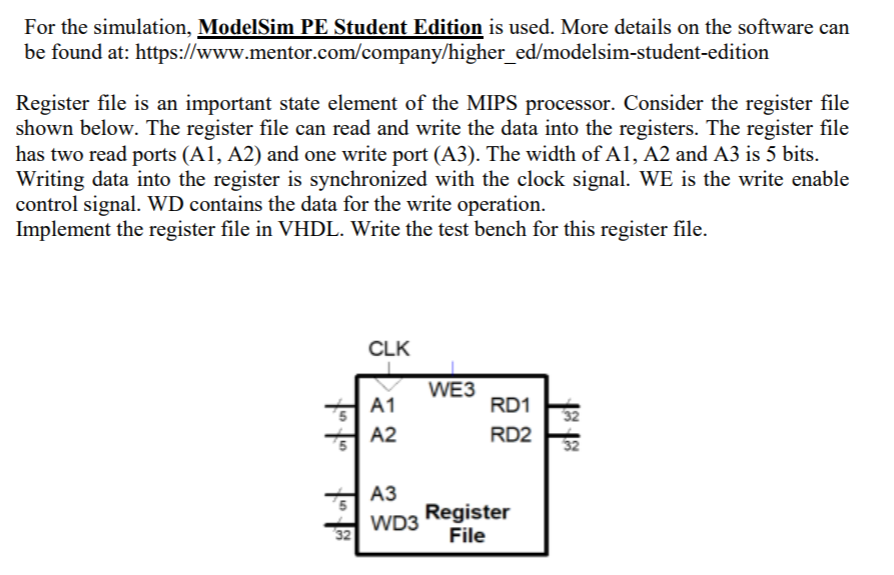

With bbox, non-changing elements can be compiled and optimized once and reused when running a modified version of the testbench. ModelSim also supports very fast time-to-next-simulation turnarounds while maintaining high performance with its new black box use model, known as bbox.

The vopt mode can also improve gate-level performance by up to 4X and capacity by over 2X. The vopt performance mode can improve Verilog and mixed VHDL/Verilog RTL simulation performance by up to 10X. The ModelSim SE voptusage mode achieves industry-leading performance and capacity through very aggressive, global compile and simulation optimization algorithms of Verilog and VHDL. ModelSim SE offers the ability to simulate very large designs through support of 64bit Windows-based platforms.

Mentor modelsim code#

ModelSim SE combines high performance and high capacity with the code coverage and debugging capabilities required to simulate larger blocks and systems and attain ASIC gate-level sign-off. Through the use of a single compiler and library system for all ModelSim configurations, employing the right ModelSim configuration for project needs is as simple as pointing your environment to the appropriate installation directory. ModelSim provides seamless, scalable performance and capabilities. The best standards and platform support in the industry make it easy to adopt in the majority of process and tool flows. The combination of industry-leading performance and capacity with the best integrated debug and analysis environment make ModelSim the simulator of choice for both ASIC and FPGA design. Mentor Graphics was the first to combine single kernel simulator (SKS) technology with a unified debug environment for Verilog, SystemVerilog, VHDL, and SystemC.

Mentor modelsim verification#

It is used in electronic design automation for development and verification of electronic (mainly digital) modules and systems for implementation on field-programmable gate arrays or integrated circuits.

Mentor modelsim software#

Mentor Graphics Corporation, a world leader in electronic hardware and software design solutions, providing products and consulting services, has presented ModelSim SE 10.5 is a popular simulator and debugging environment for VHDL, Verilog and SystemC. Mentor Graphics ModelSim SE 10.5 (64bit) | 672.1 mb

0 kommentar(er)

0 kommentar(er)